# **ЦИФРОВЫЕ ВЫЧИСЛИТЕЛЬНЫЕ СИНТЕЗАТОРЫ** –

# СОВРЕМЕННЫЕ РЕШЕНИЯ

В.Кочемасов, к.т.н., Д.Скок, А.Черкашин, к.т.н. alexander@radiocomp.ru

Неотъемлемым элементом большинства радиотехнических устройств являются системы синтеза частот и сигналов. Один из основных типов синтезаторов частот — цифровые вычислительные синтезаторы (ЦВС). Высокое разрешение по частоте и фазе, максимально быстрый переход на другую частоту без разрыва фазы, возможность управления частотой, фазой, а иногда и амплитудой по цифровому интерфейсу постоянно расширяют сферу применения ЦВС в различных областях техники (спутниковая связь, радиолокация и радионавигация, измерительные генераторы и стандарты частоты [1–3]). В статье рассказывается о технических решениях, используемых при создании современных ЦВС.

#### ОСНОВНЫЕ СВЕДЕНИЯ О ЦВС

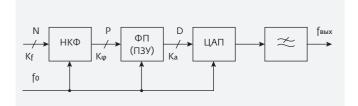

Со времени первого опубликования [4] структурная схема ЦВС не претерпела коренных изменений. В состав ЦВС (рис.1) входят следующие блоки: накопитель кода фазы (НКФ), функциональный преобразователь (ФП) фаза-синус, цифроаналоговый преобразователь (ЦАП). На выходе ЦВС ставится фильтр нижних частот (ФНЧ). Отметим, что в зарубежных источниках вместо термина ЦВС, как правило, используется близкий по содержанию термин Direct Digital Synthesizer (DDS), а для обозначения схемы ЦВС без ЦАП применяется аббревиатура NCO – Numerically Controlled Oscillator.

Процесс синтеза частоты выглядит следующим образом. НКФ формирует код фазы  $K_{\phi}$ , значение которого изменяется линейно от периода к периоду с шагом, равным коду частоты  $K_f$ . Затем код фазы преобразуется в код амплитуды  $K_a$  в соответствии с гармонической функцией. Далее на основании кода амплитуды ЦАП формирует аналоговый сигнал, который после фильтрации в ФНЧ

подается на выход. Выходная частота определяется по формуле:

$$f_{\text{BMX}} = \frac{K_f}{2^N} \cdot f_0$$

.

Если возникает необходимость управления амплитудой выходного сигнала (в соответствии с еще одним кодом –  $K_y$ ), в разрыв между функциональным и цифроаналоговым преобразователями включается перемножитель кодов  $K_a$  и  $K_y$  и на цифроаналоговый преобразователь подается код  $K_{av} = K_a K_v$ .

В истории развития ЦВС можно выделить два основных этапа.

Первый этап – с начала 70-х до конца 90-х годов прошлого века. В этот период формируются основные структуры ЦВС, проводятся работы по созданию новых схемотехнических решений и алгоритмов, обеспечивающих необходимое быстродействие и высокую точность формирования отсчетов на выходе ЦАП, апробируются различные

ТЕМА ГОДА: СВЧ

**Рис.1.** Структурная схема классического ЦВС. N, P и D – разрядности кодов частоты, фазы и амплитуды соответственно;  $f_0$  – тактовая частота;  $K_f$  – входной код частоты

виды интегральных технологий (ЭСЛ, GaAs, КМОП и др.) при создании реальных изделий. Основными производителями интегральных ЦВС на этом этапе были компании Qualcomm, Stanford Telecom и Analog Devices. Многие технические решения отрабатывались на ПЛИС. Более того, из-за отсутствия или недоступности интегральных ЦВС во многих радиоэлектронных изделиях нашли широкое применение ЦВС на ПЛИС.

Второй этап (с начала 90-х годов прошлого века и до сегодняшнего дня) знаменовался интенсивным развитием КМОП-технологии и значительным прогрессом в части построения быстродействующих многоразрядных ЦАП, цифровых интеграторов для накопителей кода фазы, схем памяти. На этом этапе также вырабатывались решения, обеспечивающие работу ЦВС с тактовой частотой в сотни или тысячи мегагерц. Коммерчески успешной среди зарубежных производителей оказалась лишь компания Analog Devices со своей линейкой ЦВС, включающей микросхему AD9914 с тактовой частотой до 3,5 ГГц [5]. Менее известна продукция компаний Teledyne Research (микросхема RDS010 с частотой тактирования до 900 МГц в керамическом корпусе) и Euvis. В России единственным конкурентом зарубежных производителей

Рис.2. Накопитель фазы

можно считать компанию ЭЛВИС. В 2011 году компания выпустила микросхему 1508ПЛ8Т [6], которая благодаря своим возможностям оказалась вполне конкурентной с продукцией Analog Devices. Можно констатировать, что появление этой микросхемы позволит решить многие задачи, возникающие при построении радиолокационных и связных комплексов.

Сегодня проводятся дальнейшие исследования и разработки, направленные, прежде всего, на увеличение тактовой частоты и улучшение спектральных характеристик ЦВС. Судя по публикациям, в основном эти исследования ведутся специалистами США, Южной Кореи, Италии, КНР. В США поставлена задача - довести тактовую частоту интегральных ЦВС до 100 ГГц. Столь амбициозные планы связаны с открывающимися стратегическими возможностями при создании перспективных радиолокационных и связных комплексов.

Рассмотрим принципы построения узлов, входящих в состав ЦВС, за исключением ФНЧ.

### НАКОПИТЕЛИ КОДА ФАЗЫ

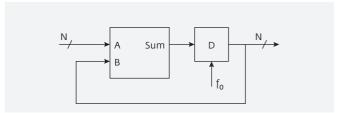

В простейшем случае N-разрядный накопитель кода фазы (НКФ) состоит из последовательно соединенных N-разрядного сумматора и регистра (элемента задержки) D (рис.2). Структура простейшего N-разрядного сумматора представляет собой цепочку из одноразрядных сумматоров.

Рис.3. Простой N-разрядный сумматор

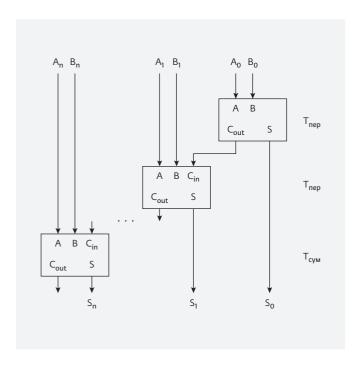

Выход разряда переноса  $C_{\rm out}$  каждого из них соединен с соответствующим входом последующего  $C_{\rm in}$  (рис.3). Поскольку значение переноса вычисляется последовательно для каждого из разрядов, общее время вычисления суммы S будет пропорционально числу разрядов слагаемых:

$$T_c = (N-1)T_{nep} + T_{cym}$$

,

где  $T_{\text{пер}}$  – время, необходимое для формирования разряда переноса,  $T_{\text{сум}}$  – время, необходимое для суммирования. Следовательно, при разрядности современных НКФ 32–48 бит их быстродействие будет крайне низким.

Основной задачей при построении НКФ является повышение скорости функционирования (тактовой частоты). Для достижения этой цели применяются конвейерные сумматоры (в иностранной литературе – pipelined adder), а также сумматоры с параллельным (ускоренным) переносом (CLA, carry look ahead), сумматоры Брента-Кунга (ВК) и схемы условного суммирования (СА). Следует отметить, что сумматоры с последовательным переносом (ripple carry adder, RCA) не нашли применения в быстродействующих накопителях кодов из-за неэффективности реализации этой структуры на высоких частотах тактирования.

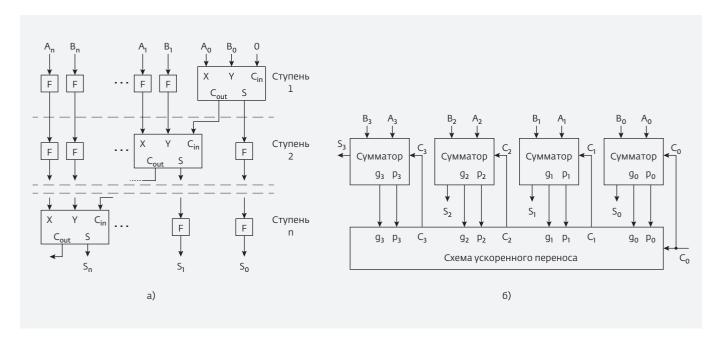

Принцип работы сумматора с конвейеризацией (рис.4а) состоит в следующем. На каждом шаге конвейера происходит суммирование одного разряда. Остальные разряды остаются неизменными и хранятся в регистрах F. В то время как происходит сложение второго разряда первой пары чисел, может начинаться суммирование первого разряда второй пары чисел. Отметим, что время суммирования одной пары по сравнению с обычным сумматором не изменяется, однако интервал изменения выходного кода сумматора теперь равен T<sub>C</sub>/n, где n – число ступеней конвейера. То есть при суммировании

Рис.4. Структурная схема конвейерного сумматора (а) и сумматора с параллельным переносом (б)

ТЕМА ГОДА: СВЧ

потока данных конвейерный сумматор в п раз быстрее обычного.

Схема сумматора с параллельным переносом (рис.4б) состоит из нескольких сумматоров с меньшей разрядностью и схемы ускоренного переноса [7]. В общем случае для сигнала переноса і-го разряда справедливо соотношение:  $C_i = g_{i-1} + p_{i-1}C_{i-1}$ . где  $g_{i-1} = A_{i-1}B_{i-1}$ ,  $p_{i-1} = A_{i-1} + B_{i-1}$ . Сигнал  $g_i$  называют функцией генерации переноса. Сигнал рі показывает, передается ли полученный в младшем разряде сигнал переноса Сі дальше, поэтому он называется функцией распространения переноса. Как следует из приведенных выражений, время формирования сигнала переноса в любой разряд с помощью вспомогательных функций gi и р<sub>і</sub> определяется только временем задержки распространения сигнала на двух логических элементах И и ИЛИ, где вычисляется значение C<sub>i</sub>.

Архитектура Брента-Кунга представляет собой также схему с ускоренным переносом, но оптимизированную по площади ИС за счет небольшого снижения быстродействия [8].

Сравнение различных реализаций НКФ (табл.1) позволяет сделать вывод, что переход от технологии 0,25 мкм к технологии 0,18 мкм дает при прочих равных условиях приблизительно троекратный выигрыш в потреблении и двукратный выигрыш в площади. Кроме того, в 1,5-2 раза повышается предельное быстродействие. С точки зрения архитектуры наилучшими характеристиками обладают сумматоры с ускоренным переносом (CLA) и сумматоры Брента-Кунга. Архитектура условного суммирования (СА) дает,

как правило, худшие результаты как по площади ИС, так и по быстродействию. Следует отметить, что выбор той или иной архитектуры зависит от многих факторов: разрядности накопителя, соотношения тактовой частоты и задержки в различных логических элементах, критериев оптимизации (по площади, быстродействию, потребляемой мощности в динамическом режиме, мощности токов утечки) и др.

## ФУНКЦИОНАЛЬНЫЕ ПРЕОБРАЗОВАТЕЛИ

В классическом ЦВС (см. рис.1) функциональный преобразователь реализован на основе ПЗУ, хранящего табличную функцию синуса. Желание повысить точность преобразования фазы в синус (косинус), а значит, улучшить спектральные характеристики выходного сигнала ведет к существенному увеличению объема памяти и, как следствие, к увеличению энергопотребления и снижению быстродействия. Практическое применение нашли два способа построения ФП, позволяющие добиться улучшения характеристик ЦВС: сокращение объема ПЗУ (компрессия) и использование аппроксимационных вычислительных методов. Кроме того, используются комбинации этих способов.

Простейший способ уменьшения необходимого объема памяти заключается в использовании свойства симметричности функции синуса. При этом в ПЗУ записываются значения синуса на интервале, равном четверти периода (квадранте), т.е. вместо функции sin(p·2π) используют функцию  $\sin(p \cdot \pi/2)$ , где  $0 \le p \le 1$ . При этом

Таблица 1. Сравнение различных архитектур построения накопителей кодов фазы

| Технологиче-<br>ский процесс,<br>мкм | Архитектура | Максималь-<br>ная рабочая<br>частота, МГц | Потребл               | Площадь               |                       |                                   |

|--------------------------------------|-------------|-------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------------------|

|                                      |             |                                           | на частоте<br>100 МГц | на частоте<br>250 МГц | на частоте<br>500 МГц | устрой-<br>ства, мкм <sup>2</sup> |

| 0,25                                 | CLA         | 380                                       | 10,9                  | 27                    | _                     | 36 247                            |

| 0,25                                 | ВК          | 450                                       | 11                    | 27,6                  | _                     | 35 308                            |

| 0,25                                 | CA          | 360                                       | 12                    | 30                    | _                     | 41 587                            |

| 0,25                                 | RCA         | 260                                       | 10,8                  | 27,2                  | _                     | 33 563                            |

| 0,18                                 | CLA         | 510                                       | 4,3                   | 10,8                  | 21,6                  | 22103                             |

| 0,18                                 | ВК          | 510                                       | 4,4                   | 11,1                  | 22,3                  | 23 284                            |

| 0,18                                 | CA          | 497                                       | 4,68                  | 11,7                  | 23,4                  | 25 862                            |

код фазы на входе  $\Phi\Pi$  уменьшается на два разряда (Q = P-2).

Формирование полного периода гармонической функции возможно также, если известно ее значение на интервале  $[0, \pi/4]$  [9]. В этом случае используются два ПЗУ, где хранятся табличные значения функций sin и соз на данном интервале. Если требуется, например, найти отсчеты гармонической функции во втором октанте (интервал  $[\pi/4, \pi/2]$ ), для изменения знака входного кода производится его двоичное дополнение. Кроме того, выходные сигналы меняются местами, при этом отсчеты берутся из блока со значениями косинуса, т.к.  $\cos(\pi/4+x)=\sin(\pi/4-x)$ . Подобные операции выполняются для получения значений гармонической функции во всех октантах, кроме первого.

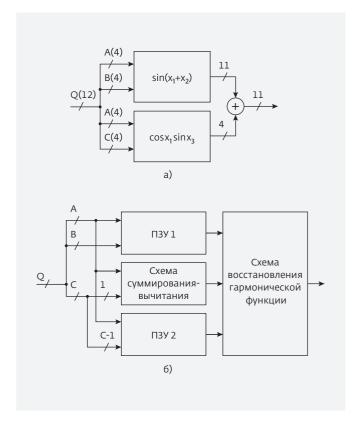

Большое количество методов сжатия памяти основано на применении интерполяции синусоидальной функции. В этом случае один блок памяти разбивается на два или более блоков. Такой способ был предложен Сандерлендом [10]. Пусть блок памяти без сжатия имеет разрядность 12 бит. Эта разрядность (от старшего разряда к младшему) разбивается на три сегмента – А, В и С – по четыре бита каждый со следующими значениями фазы:

$$x_1 < \frac{\pi}{2}; x_2 < \frac{\pi}{2^5}; x_3 < \frac{\pi}{2^9}$$

. Результирующее значение

синусоидальной функции приближенно находится из выражения:

$$f_{a\pi\pi p}(x) = \sin(x_1 + x_2) + \cos x_1 \sin x_3$$

.

Таким образом, исходный блок памяти разделяется на два блока с восьмибитной адресацией (рис.5а): ПЗУ, содержащее 11-разрядные отсчеты первого слагаемого, и ПЗУ, в котором расположены четырехразрядные отсчеты второго слагаемого. Такой способ позволяет уменьшить объем требуемой памяти в 11,7 раза.

Альтернативный способ с двумя ПЗУ был предложен Николасом (Nicholas) (рис.5б) [11]. В нем, как и в архитектуре Сандерленда, фазовое слово разбивается на три, с разрядностями А, В и С. Квадрант гармонической функции разбивается по фазе на 2<sup>A</sup> интервалов, а каждый из них – на 2<sup>B</sup> подынтервалов. Приближенное значение синуса получается на основе отсчетов, хранимых в ПЗУ 1, на вход которого поступают значения старших разрядов фазы А+В. Далее происходит уточнение значений синуса путем добавления или вычитания поправочных значений, хранимых в ПЗУ 2,

на вход которого поступают слова А и С. За счет использования схемы суммирования и вычитания (вместо простого суммирования, как в схеме Сандерленда) и в силу того, что абсолютные значения положительных и отрицательных поправок равны, объем ПЗУ уменьшается в два раза.

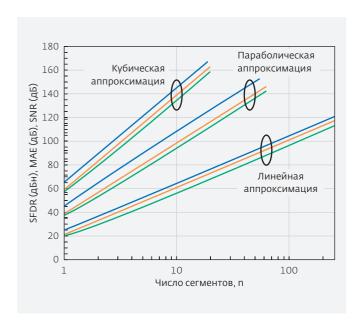

Большая группа работ по реализации ФП посвящена методам полиномиальной аппроксимации гармонической функции. Существуют несколько критериев оптимальности выбора аппроксимирующего полинома. Так, по критерию минимума абсолютной ошибки формирования сигнала (отличия формируемой гармонической функции от эталонной, МАЕ) оптимальным является использование полиномов Чебышева [12]. Полиномы Лежандра оптимальны с точки зрения минимизации соотношения сигнал/шум (SNR) [13]. Максимум значения наибольшего динамического диапазона, свободного от побочных дискретных составляющих (SFDR), можно получить, например, используя минимизацию членов (кроме основной гармоники) в разложении выходного сигнала ЦВС в ряд Фурье.

Большинство работ в этой группе реализует общий подход: один квадрант гармонической

Рис.5. Архитектуры Сандерленда (а) и Николаса (б)

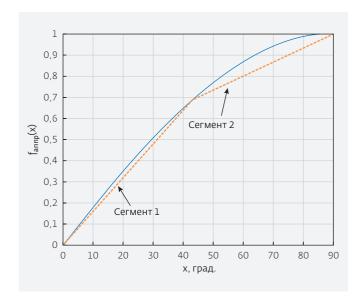

**Рис.6.** Предельные значения SFDR (синяя линия), MAE (зеленая линия) и SNR (оранжевая линия)

функции равномерно или неэквидистантно разбивается по фазе на п сегментов, внутри которых производится интерполяция гармонической функции отрезками полиномиальных функций различных порядков. С ростом порядка полинома и числа сегментов существенно улучшаются потенциальные значения показателей качества формирования сигнала (рис.6) [14]. Однако при этом возрастает сложность практической реализации ФП, что негативно сказывается на быстродействии ЦВС. Нахождение полиномиальных коэффициентов при оптимизации по критерию минимума SFDR часто производят с помощью метода Нелдера-Мида [15]. Для упрощения аппаратной реализации ФП применяются

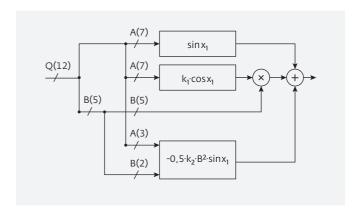

**Рис.7.** Структурная схема аппроксимации гармонической функции рядом Тейлора второго порядка

специальные алгоритмы вычисления полиномиальных функций и способы построения вычислительных узлов. Далее рассмотрены различные варианты полиномиальной интерполяции. Следует отметить, что во многих зарубежных работах, посвященных способам построения ФП, ЦАП является внешним устройством и не включается в состав тестовой ИС. Таким образом, значения SFDR, приведенные в этом разделе, непосредственно отражают вклад ФП в данный параметр.

Один из способов реализации функционального преобразователя основан на аппроксимации (интерполяции) синусоидальной функции рядом Тейлора [16]. При этом входной код фазы Q делится на два двоичных слова: A, содержащее старшие разряды, и B = Q - A, включающее младшие разряды. Ряд Тейлора раскладывается вокруг значений  $x_1$ , соответствующих старшим разрядам фазы:

$$f_{annp}(x) = \sin x_1 + k_1 \cdot B \cdot \cos x_1 - \frac{k_2 \cdot B^2 \cdot \sin x_1}{2} + \dots,$$

где  $\frac{\pi}{2^{B+1}}$  <  $x_1 \le \frac{\pi}{2}$  . Таким образом, одно ПЗУ заменя-

ется на два при линейной аппроксимации и на три - при квадратичной (рис.7).

В методе равных сегментов [17] четверть периода гармонической функции разбивается на п эквидистантных сегментов (рис.8а). При этом значение амплитуды на выходе  $\Phi\Pi$  записывается в виде:  $f_{annp}(x) = b(k) + \Delta x m(k)$ , где k = 0, 1, ..., n-1 – номер сегмента,  $b(k) = \sin(\pi k/(2n))$  – начальное значение

амплитуды в каждом сегменте,  $x_0 = \frac{\pi K_{\Phi\Pi}}{2^{Q+1}}$  – значе-

ние фазы, определяемое кодом  $K_{\Phi\Pi}$  на входе функционального преобразователя,  $K_{\Phi\Pi}$  = 0, 1, 2, ...,  $2^{Q}$  – 1,

$\Delta x = x_0 - \frac{\pi k}{2n}$  – разность фаз между заданным значе-

нием фазы на входе ФП и начальным значением

фазы в сегменте,  $m(k) = \frac{\left[b(k+1) - b(k)\right]}{\Delta k}$  – наклон

аппроксимирующего отрезка,  $\Delta k = \frac{\pi}{2n}$  - длина сег-

мента. Описанный метод реализуется с помощью трех ПЗУ (рис.8б), в которых хранятся коэффициенты b(k), m(k) и значения коэффициентов компенсации ошибок аппроксимации гармонической функции  $D(x) = \sin(x) - f_{annp}(x)$ . Разрядность

ТЕМА ГОДА: СВЧ

Рис.8. Иллюстрация метода равных сегментов (а) и структурная схема ФП на основе этого метода (б)

и объем ПЗУ 3, в котором хранятся коэффициенты D(x), определяется числом сегментов и требуемой точностью воспроизведения гармонической функции. Показано [17], что этот способ позволяет уменьшить объем требуемой памяти в десять раз.

Метод, описанный в [9], подразумевает, что в каждом из сегментов аппроксимирующая функция представляет собой два линейных отрезка, имеющих разный наклон и общую точку в середине данного сегмента.

В [18] представлена аппроксимация косинусоидальной функции следующего вида:

$$f_{a\pi\pi p}(x) = 0,99941104599607-1,22565453358226 x^2 + 0,22882340561354 x^4.$$

Соответствующая этой аппроксимации схема NCO позволяет получить значение SFDR = 72,2 дБн.

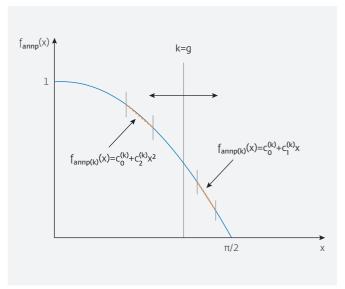

Квазилинейный полиномиальный метод интерполяции гармонической функции [19] подразумевает сочетание кусочно-линейной и кусочно-параболической аппроксимации.

Рис.9. Иллюстрация квазилинейного метода интерполяции

Для каждого сегмента разбиения квадранта аппроксимирующая функция имеет вид:

$$f_{\mathrm{annp}(k)}\!\left(x\right)\!=\!\begin{cases} c_0^{(k)}\!+\!c_2^{(k)}x^2, & 1\!\leq\! k\!\leq\! g\\ c_0^{(k)}\!+\!c_1^{(k)}x, & g\!+\!1\!\leq\! k\!\leq\! n, \end{cases},$$

где k - номер сегмента,  $c_0$ - $c_2$  - полиномиальные коэффициенты, выбираемые из условия максимума SFDR во всем рабочем диапазоне частот, и д - номер сегмента, в котором происходит смена вида полинома от линейного к параболическому и наоборот (рис.9). Этот

Рис.10. Двухсегментная аппроксимация синусоидальной функции

Таблица 2. Характеристики ФП, представленных в зарубежных публикациях

| Ссылка<br>на<br>публика-<br>цию | Метод<br>построения<br>ФП                              | Разрядность<br>накопителя<br>фазы, бит | Технологиче-<br>ский процесс<br>изготовления<br>СБИС, мкм | SFDR,<br>дБн | Макси-<br>мальная<br>тактовая<br>частота,<br>МГц | Потреб-<br>ляемая<br>мощность,<br>мкВт/МГц |

|---------------------------------|--------------------------------------------------------|----------------------------------------|-----------------------------------------------------------|--------------|--------------------------------------------------|--------------------------------------------|

| [14]                            | Кусочно-линейная<br>аппроксимация, n=64                | 24                                     | 0,25                                                      | 83,6         | 526                                              | 102                                        |

| [23]                            | Уменьшение объема ПЗУ                                  | 24                                     | 0,25                                                      | 80           | 714                                              | 64,5                                       |

|                                 | уменьшение ооъема 1139                                 |                                        |                                                           | 101          | 201                                              | 61,7                                       |

| [17]                            | Уменьшение объема ПЗУ                                  | 32                                     | 0,25                                                      | 85           | _                                                | _                                          |

| [9]                             | Кусочно-линейная<br>аппроксимация с двумя<br>наклонами | 24                                     | 0,25                                                      | 80           | 600                                              | 127                                        |

| [18]                            | Полиномиальная аппрок-<br>симация 4-го порядка         | 24                                     | 0,13                                                      | 72,2         | 210                                              | 11,6                                       |

| [19]                            | Квазилинейная<br>интерполяция                          | 24                                     | 0,13                                                      | 89           | 178                                              | 13,8                                       |

| [20]                            | Неэквидистантная кусочно-линейная аппроксимация        | 24                                     | 0,13                                                      | 90,3         | 1000                                             | 10,2                                       |

| [21]                            | Полиномиальная аппрок-<br>симация 8-го порядка         | 16                                     | 0,18                                                      | 95           | 500                                              | 160                                        |

| [22]                            | Двухсегментная аппрокси-<br>мация 4-го порядка         | 32                                     | 0,25                                                      | 90           | 200                                              | 410                                        |

метод учитывает тот факт, что вблизи значения x=0 функция косинуса сходна по форме с параболой, в то время как при приближении к значению  $x=\pi/2$  функция все ближе к прямой линии.

Аппроксимация гармонической функции может быть также выполнена с помощью неэквидистантной кусочно-линейной интерполяции [20]. В таком методе гармоническая функция представляется совокупностью нескольких линейных сегментов различной длины. Этот способ требует значительно меньшего количества сегментов по сравнению с интерполяцией сегментами равной длины при одинаковых значениях SFDR. Так, например, для получения SFDR=84,2 дБн необходимо 17 сегментов с различной длиной или 32 равных сегмента.

В работе [21] использовалась полиномиальная аппроксимация 8-й степени. После приведения к виду, удобному для практической реализации, выражение для такой аппроксимации имеет вил:

$$\begin{split} f_{annpq}(x) &= 1 - \frac{1}{2} x^2 + \left( c_{q1} x^2 - c_{q2} x^4 \right)^2, \quad 0 \leq x \leq \pi/2 \ . \\ c_{q1} &= \frac{835}{2^{12}}, \ c_{q2} = \frac{53}{2^{14}}. \end{split}$$

В [22] представлена двухсегментная аппроксимация гармонической функции, в которой один сегмент определяется на интервале [0,  $\pi$ /4], а второй – на интервале [ $\pi$ /4,  $\pi$ /2] (рис.10):

$$f_{annp}(x) = \begin{cases} c_{1,1} \cdot x^4 + c_{1,2} \cdot x^3 + c_{1,3} \cdot x^2 + c_{1,4} \cdot x + c_{1,5}, & 0 \le x \le \pi/4 \\ c_{2,1} \cdot x^4 + c_{2,2} \cdot x^3 + c_{2,3} \cdot x^2 + c_{2,4} \cdot x + c_{2,5}, & \pi/4 \le x \le \pi/2. \end{cases}$$

В результате реализации этого метода получено значение SFDR = 90 дБн.

Таким образом, существует множество способов построения функциональных преобразователей (табл.2). Разработчики продолжают создавать новые варианты, стремясь минимизировать уровень паразитных составляющих в выходном сигнале и максимально повысить рабочую частоту.

Продолжение следует.

#### ЛИТЕРАТУРА

- 1. **Кочемасов В.Н., Белов Л.А., Оконешников В.С.** Формирование сигналов с линейной частотной модуляцией. М.: Радио и связь, 1983.

- 2. **Кочемасов В.Н., Долбня Е.В., Соболь Н.В.** Акустоэлектронные Фурье-процессоры. М.: Радио и связь, 1987.

- 3. **Walls F.L.** Local oscillator requirements and strategies for the next generation of high-stability frequency standards. Proc. 1992 IEEE Freq. Contr. Symposium. USA, 1992, p.2-5.

- 4. **Tierney J., Rader C.M., Gold B.** A digital frequency synthesizer. IEEE Trans. Audioelectroacoust, March 1971, vol.Au-19, p.48.

- 5. AD9914. Data Sheet. Analog Devices, 2014. www.analog.com/static/imported-files/data\_sheets/AD9914.pdf.

- 6. Микросхема интегральная 1508ПЛ8Т. Техническое описание. 2012, http://multicore.ru/index.php?id=466.

- 7. **Bhupatiraju R.D.** A comparative study of high speed adders. Ohio University, 1999.

- 8. **Ibrahim S.H., Ali S.H.M., Islam M.S.** High speed direct digital frequency synthesizer with pipelining phase accumulator based on Brent-Kung adder. ICSE, 2012, p.547-550.

- 9. **De Caro D., Strollo A.G.M.** High-performance direct digital frequency synthesizers in 0.25 mm CMOS using dual-slope approximation. IEEE J. Solid-State Circuits, Nov.2005, vol.40, no.11, p.2220-2227.

- 10. **Sunderland D.A., Strauch R.A., Wharfield S.S.** et al. CMOS/SOS frequency synthesizer LSI circuit for spread spectrum communications. IEEE J. of Solid State Circuits, Aug. 1984, vol.SC-19, p.497–505.

- 11. **Vankka J., Halonen K.** Direct digital synthesizers. theory, design and applications. Boston: Kluwer Academic, 2001.

- 12. **Ashrafi A., Adhami R., Joiner L., Kaveh P.**Arbitrary waveform DDFS utilizing Chebyshev polynomials interpolation. IEEE Trans. Circuits and Systems, 2004, vol.51, no.8, p.1468-1475.

- 13. **Wen C.-H., Hsu H.-Y., Ko H.Y., Wu A.-Y.** Least squares approximation-based ROM-free direct digital frequency synthesizer. Proceedings of ISCAS '04, 2004, p.II-701-II-704.

- 14. **De Caro D., Strollo A.G.M.** High-performance direct digital frequency synthesizers using piecewise-polynomial approximation. IEEE Trans. Circuits Syst. I, Feb. 2005, vol.52, p.324-336.

- 15. **De Caro D., Napoli E., Strollo A.G.M.** Direct digital frequency synthesizers with polynomial hyperfolding technique IEEE Trans. Circuits Syst. II Exp. Briefs, Jul. 2004, vol.51, no.7, p.337-344.

- 16. **Palomaki K.I., Niittylahti J.** Methods to improve the performance of quadrature phase-to-amplitude conversion based on Taylor series approximation. Proceedings of the 43rd IEEE Midwest Symposium on Circuits and Systems, 2000, p.14-17.

- 17. **Shiann-Shiun J., Hsing-Chen L., Chen-Yu W.**High-performance DDFS design using the equisection division method. IEEE Transactions on Ultrasonics Ferroelectrics and Frequency Control, Dec. 2010, vol.57, no.12, p.2616–2626.

- 18. **Ashrafi A., Adhami R.** Theoretical upperbound of the spurious free dynamic range in direct digital frequency synthesizers realized by polynomial interpolation methods. IEEE Trans. Circuit Syst. I, Reg.Papers, Oct. 2007, vol.54, no.10, p.2252-2261

- 19. **Ashrafi A., Adhami R., Milenkovic A.** A direct digital frequency synthesizer based on the Quasilinear interpolation method. IEEE Trans. Circuit Syst. I, Reg. Papers, Apr. 2010, vol.57, no.4, p.863-872.

- Caro D., Petra N., Strollo A. Direct digital frequency synthesizer using nonuniform piecewise-linear approximation. IEEE Trans. Circuit Syst. I, Reg. Papers, Oct. 2011, vol.58, no.10, p.2409-2419.

- 21. **Chen Y.H., Chau Y.A.** A direct digital frequency synthesizer based on a new form of polynomial approximations. IEEE Trans. Consum. Electron., May 2010, vol.56, no.2, p.436-440.

- 22. Li Xiaojin, Lai Linhui, Lei Ao, Lai Zongsheng.

A direct digital frequency synthesizer based on two segment fourth-order parabolic approximation. IEEE Transactions on Consumer Electronics, June 2009, p.322-326.

- 23. **De Caro D., Petra N., Strollo A.G.M.** Reducing look-up table size in direct digital frequency synthesizers using optimized multipartite table method. IEEE Trans. Circuits Syst. I, Reg. Papers, Aug. 2008, vol.55, no.7, p.2116-2127.